Удивительной особенностью транзисторов, которой индустрия информационных технологий обязана своим бурным ростом, является то, что их производительность увеличивается одновременно с тем, как стоимость и размеры уменьшаются. Единственное устройство, имеющее такую же особенность при сравнимых темпах уменьшения габаритов – магнитные диски. Современные транзисторы в 20 раз быстрее и в 100 с лишним раз меньше, чем те, что выпускались два десятилетия лет назад. Даже на интуитивном уровне понятно, что такое положение дел не может сохраняться вечно. Однако даже самым проницательным аналитикам до сих пор не удавалось точно спрогнозировать, каким будет предельный минимальный размер транзистора. Этот прогнозируемый предел отодвигался все дальше примерно с той же скоростью, с какой уменьшались реальные размеры транзисторов. Поэтому точность и моих собственных прогнозов относительно будущего технологий КМОП вряд ли будет очень высокой. Однако знание базовых принципов развития технологии позволяет до некоторой степени судить о ее будущем.

Как показало недавнее исследование, проведенное Тауром и др. [1], темпы роста производительности наиболее часто используемых в настоящее время транзисторов (комплементарные полевые транзисторы, называемые «КМОП») по мере уменьшения их размеров вскоре снизятся. Пути поддержания темпов роста производительности Таур рекомендует искать в транзисторах новых типов, в низкотемпературном режиме работы и повышении степени интеграции функций. В данной статье анализируются эти и другие проблемы развития технологии КМОП. Обосновывается вывод, что нынешние темпы повышения производительности можно сохранить еще в течение 10-15 лет, но только посредством поиска новых материалов и структур транзисторов. Кроме того, чтобы транзисторы продолжали уменьшаться в размерах, необходимы коренные изменения в литографии. Технология, на которой основаны модули динамической оперативной памяти (DRAM), также приближается к пределу своих возможностей, и для перехода барьера в 1 Гбит потребуется разработка новой архитектуры.

Чаще всего для описания эволюции технологии КМОП применяется так называемый «закон Мура». Важно понимать предположения, на которых он базируется, так как это позволит нам заглянуть в будущее. В 1965 году Гордон Мур заметил, что число элементов наиболее сложной из существующих интегральных схем ежегодно удваивается. В 1959 году появился первый планарный транзистор, а в 1965-м уже выпускались микросхемы, состоящие из 50-60 элементов. Тогда Мур дал прогноз, согласно которому эта тенденция должна была сохраниться в течение последующих 10 лет [2], и в 1975 году с удивлением заметил, что он сбылся [3]. Согласно новому прогнозу Мура через некоторое время темпы удвоения числа элементов интегральных схем должны были замедлиться вдвое. По мнению Мура, это снижение темпов роста числа элементов должно было произойти в 1980 году, но оно случилось раньше, уже в 1975-м. За последние 20 лет прогноз Мура получил широкую известность и приобрел статус «закона». Термин «закон Мура» стали употреблять для обозначения непрерывного экспоненциального роста функциональности интегральных схем с одновременным снижением их стоимости.

Значение закона Мура кроется не в постоянстве темпов роста числа элементов, а в глубинных причинах этой тенденции и ее следствиях. В своем первоначальном прогнозе Мур указал, что удвоение числа элементов в интегральных схемах будет происходить за счет трех факторов: на 50% – за счет увеличения разрешающей способности литографии; на 25% – за счет увеличения размера кристалла благодаря улучшению производственных процессов и литографии; и на остающиеся 25% – за счет разного рода инноваций, в частности появления новых методов формирования элементов на кристалле (из которых подавляющее число составляют транзисторы). Эти три фактора являются движущими силами тенденции к увеличению числа элементов на кристалле.

Основываясь на предположении, что расходы на производство кристалла будут расти медленнее, чем число элементов, Мур указал также, что результатом роста числа элементов на кристалле станет снижение стоимости на элемент. Результирующее экспоненциальное снижение стоимости на функцию и является реальной движущей силой развития полупроводниковой индустрии и информационных технологий в целом. Суть не в постоянстве темпов роста числа элементов, а в том, что темпы увеличения числа элементов (и функций, соответственно) – выше, чем темпы роста стоимости производства кристалла. Темпы удвоения в законе Мура были пересмотрены однажды в прошлом, и могут измениться вновь, но пока стоимость в пересчете на функцию падает, информационная революция будет продолжаться.

Производительность в законе Мура напрямую не упоминается. Однако с ростом числа транзисторов ассоциируется именно повышение производительности. Правда, одно из другого автоматически не следует. Повышение производительности процессора происходит за счет увеличения плотности упаковки интегральных схем и совершенствования конструкции транзистора.

Ключ к успешному прогнозированию будущего технологий КМОП лежит в понимании факторов, влияющих на величину стоимости на функцию. КМОП будет доминировать и развиваться до тех пор, пока себестоимость на функцию будет падать. Мы рассмотрим следующие важнейшие составляющие этой тенденции.

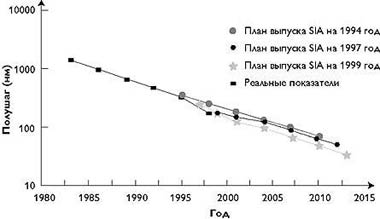

Литография – это метод переноса рисунка с фотошаблонов на кремниевые пластины. Ее совершенствование — основная движущая сила уменьшения размера транзисторов. На рис. 1 показаны графики прогнозировавшегося и реального роста разрешающей способности литографического процесса. Когда-то считалось, что предел возможностей оптической литографии (в которой засветка производится излучением с длиной волны, примерно соответствующей видимому свету) – чуть более 1 микрона, но уже сейчас индустрия освоила величину в 0,18 микрон. Интересно отметить, что прогресс последнего времени превзошел большинство прогнозов.

|

| Рис. 1. Сложившиеся и новые тенденции в изменении разрешающей способности литографического процесса. Здесь полушаг – это минимальный размер литографических параметров на кристалле. (SIA – Semiconductor Industry Association) |

Литографию можно характеризовать, в частности, минимальной толщиной линий (раздельно воспроизводимых параллельных отверстий в маске) в сравнении с длиной волны излучения, используемого для экспонирования. Первоначально в качестве источников наиболее широко применялись ртутные лампы. Толщина линий, формируемых при помощи такого процесса, была больше, чем длина волны излучения. В последние годы стандартными стали так называемые линия g и линия i в спектре ртути с длинами волны 435 и 365 нм соответственно. При помощи источника излучения с длиной волны 365 нм вычерчиваются линии толщиной до 0,35 микрон, что почти соответствует длине волны. Затем благодаря переходу на источники, действующие в спектре глубокого УФ-излучения (ртутные лампы, или эксимерные лазеры [excimer laser], которые в последнее время применяются чаще) с длиной волны 248 нм, стало возможным вычерчивать 0,25-микронные линии, т.е. опять же соответствующие длине волны. Сейчас полупроводниковая промышленность переходит на 0,18-микронную литографию: на данном этапе впервые удалось реализовать возможность вычерчивания линий с толщиной, меньшей длины волны излучения, при помощи которого происходит засветка. В дальнейшем необходимо развивать это достижение и/или далее уменьшать длину волны, возможно за счет применения принципиально новых источников.

Вычерчивание линий с толщиной, меньшей длины волны источника излучения, серьезно затрудняется дифракцией света. Следовательно, для совершенствования литографического процесса критически важно разработать методики коррекции эффектов, возникающих при приближении источника к пластине. Переход на размеры, меньшие длины волны, стал возможным благодаря различным специальным методикам, таким как внеосевое освещение (off-axis illumination) и маскирование с фазовым сдвигом (phase-shift masking). Однако их применение требует более сложных и дорогих в изготовлении масок, а также может налагать определенные конструктивные ограничения. В теории возможно формирование линий с толщиной, вдвое меньшей по сравнению с длиной волны. Для достижения высокой разрешающей способности литографии также очень важны свойства светочувствительного полимера, подвергаемого облучению.

Достижение топологических размеров в 100 нм и меньше, таким образом, по-видимому, потребует уменьшения длины волны излучения. Индустрия готовится к переходу от длины волны 248 нм (эксимерные KrF-лазеры) к 193 нм (эксимерные ArF-лазеры). Дальнейшие перспективы не ясны. Возможно, следующим шагом станет длина волны 157 нм (эксимерные F-лазеры). Однако лишь немногие материалы обладают достаточной прозрачностью для использования в рефракционных линзах или масках. Основные кандидаты обладают коэффициентом теплового расширения, в десятки раз большим, чем у кварца, поэтому искажений избежать будет очень трудно. Для масок можно было бы применять особые виды кварца, но приемлемые фоторезистивные материалы для излучения с подобной длиной волны пока еще не найдены.

Изучается возможность применения неоптических методов литографии. В частности, очень маленькие элементы позволяет формировать электроннолучевая литография, так как длина волны электронов составляет всего около 0,01 нм. Электроннолучевая литография давно используется для изготовления масок и низкоскоростного экспонирования. Однако изготовление сложных схем с применением электроннолучевой литографии потребует гораздо большей скорости экспонирования. Изучаются возможности достижения достаточной скорости за счет использования толстых электронных пучков с блокирующими масками и электрооптическими уменьшающими линзами. К подобным проектам относятся, в частности, PREVAIL [4] и SCALPEL [5]. Основные проблемы, подлежащие решению, связаны с совмещением полей (для покрытия одного кристалла требуется несколько масок), целостностью масок и их стоимостью.

В IBM для формирования экспериментальных интегральных схем с топологическими размерами от 1 до 0,15 мкм применяется контактная рентгеновская литография. Длина волны 1,1 нм выделяется из спектра синхротронного излучения, получаемого, например, в накопительном кольце Helios, построенного компанией Oxford Instruments и установленного в центре технологических исследований IBM в Ист-Фишкил (штат Нью-Йорк). Основная проблема в том, что для излучения с такой длиной волны не существует линз и зеркал. Поэтому приходится применять шаблоны с рисунком схемы в масштабе 1:1. Изготовление таких шаблонов без искажений – чрезвычайно трудоемкий и дорогостоящий процесс. В числе других проблем – необходимость расположения маски в тесной близости (10 нм или ближе) от пластины и возникающие в связи с этим эффекты дифракции. В рентгеновской проекционной литографии, называемой также EUV-литографией (по применяемому ультрафиолетовому вакуумному излучению), проблему масштаба шаблона обходят за счет излучения с длиной волны 11-13 нм. При такой длине волны становится возможным использование фокусирующей системы с четырехкратным уменьшением. Однако для такой системы необходимы вогнутые линзы, изготовленные с использованием около 40 слоев специальной пленки толщиной в 2-3 нм.

На более ранних стадиях изучения находятся другие подходы – ионно-лучевая литография и литография, основанная на излучении горячих электронов. Однако сегодня вероятность широкого применения этих методов в дальнейшем мала, а на осуществление соответствующих проектов требуются крупные инвестиции. Вывод – развитие литографии, основной составляющей закона Мура, столкнется в ближайшие годы с огромными проблемами. В частности, потребуются радикальные изменения, чтобы перейти к меньшим длинам волны излучения в оптических видах литографии. Исследования в области неоптических типов литографии пока находятся на слишком ранней стадии. Наибольший риск здесь в том, что стоимость новой системы перекроет обеспечиваемые ею преимущества в плотности упаковки элементов. В то время как стоимость излучающей системы может быть амортизирована за счет массового производства, расходы на изготовление масок должны окупаться на каждом изделии. Закон Мура сохранит свое действие только в том случае, если стоимость на элемент продолжит снижаться.

Там, где требовалась высокая производительность, со времени своего изобретения в 1948 году всегда применялись биполярные транзисторы. Вскоре после биполярного был продемонстрирован полевой транзистор, но оказалось, что скорость переключения у него ниже. Тем не менее, он достаточно широко применялся в интегральных схемах высокой плотности и малого энергопотребления. Оба типа транзисторов при уменьшении размеров работали быстрее и потребляли меньше энергии. Однако потребляемая мощность схем на биполярных транзисторах уменьшалась медленнее. Когда в начале 90-х топологические размеры интегральных схем достигли полумикронного уровня, более высокая плотность, свойственная КМОП-схемам на полевых транзисторах, стала перевешивать обеспечиваемое биполярными транзисторами преимущество в мощности. Интегрированная функциональность оказалась более важным свойством, чем высокая мощность транзистора, и поэтому сегодня подавляющее большинство выпускаемых схем основано на КМОП.

Эволюция транзистора, применяемого в КМОП-схемах, была с поразительной точностью спрогнозирована в 1972 году на Международной конференции по электронным устройствам. Группа Деннарда из Исследовательского центра IBM Томаса Уотсона представила на конференции доклад по конструкции транзисторов очень маленьких размеров [6]. Изложенной ими теории пропорционального уменьшения размеров транзисторов индустрия следует до сих пор. Согласно этой теории, для любого уменьшения топологических размеров [альфа], можно подобрать такие напряжение питания и уровень легирования, чтобы производительность повысилась в α раз, потребляемая мощность – снизилась в α2 раз, а удельная мощность осталась на прежнем уровне. В 1974 году Деннард и др. опубликовали проект транзистора с 1-микронным каналом, а также результаты исследований, проведенных над экспериментальными транзисторами. Однако подобные устройства начали выпускаться лишь через десять с лишним лет.

На практике пороговые напряжения невозможно уменьшить, не снижая рабочей температуры, и со временем удельная мощность несколько увеличилась, но в целом базовые принципы теории выполнялись. Пороговые напряжения не понижаются в основном потому, что приходится брать в расчет ток выключения. В идеальном случае при снижении напряжения рабочая температура транзистора уменьшалась бы таким образом, что ток выключения оставался бы на постоянном уровне. На практике ради сохранения рабочей температуры на уровне комнатной или выше приходится приносить в жертву часть тока выключения и держать пороговое напряжение на уровне 0,3 В или выше. Поэтому, чтобы достичь повышения производительности за счет удельной мощности, напряжение источника питания всегда делали более высоким, чем предписывалось теоретическими выкладками относительно миниатюризации.

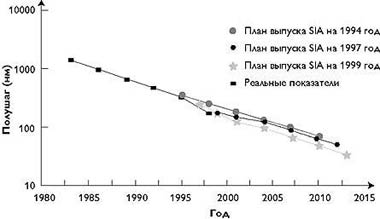

Процесс уменьшения размеров транзисторов вскоре неминуемо достигнет той точки, когда для достижения большей производительности больше нельзя будет уменьшать напряжения без существенного понижения рабочей температуры. На рис. 2 показано прогнозируемое замедление темпов повышения производительности технологии КМОП.

|

| Рис. 2. Сравнение производительности устройств,

созданных на основе последовательных поколений технологии, по годам, в

которых каждое из поколений технологии достигло уровня массового

производства Точками и проходящей через них сплошной линей указаны реальные и прогнозируемые результаты. Пунктирная линия представляет кривую экспоненциального роста, построенную в соответствии с законом Мура. В этой диаграмме относительной производительности не учитываются особенности микросхем, такие как нагрузка. |

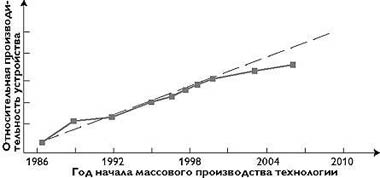

Потенциальное влияние замедления роста производительности на тактовую частоту микропроцессоров показано на рис. 3. Тактовая частота повышается, отчасти, за счет мощности транзистора, отчасти – за счет совершенствования логики и конструкции интегральной схемы. Сплошная линия предполагает, что обе тенденции сохранят прежние темпы, и таким образом к 2010 году, возможно, появятся 20-гигагерцевые процессоры. Нижняя кривая показывает, что произойдет, если после 1 ГГц мощность транзисторов будет расти в соответствии с рис. 2, а логика и конструкция схем совершенствоваться не будут. Результатом станет 1,5-гигагерцевый предел для процессоров. Наиболее же вероятный сценарий – появление новых материалов для транзисторов, а также совершенствование схем приведет к тому, что частота будет повышаться и далее, но вероятно, с меньшей скоростью, как показано на рис. 3. С учетом возможности совершенствования систем за счет прогресса в области программного обеспечения и механизмов ввода-вывода, данный темп развития, по-видимому, будет достаточным для сохранения действия закона Мура.

|

| Рис. 3. Прогнозируемая тенденция изменения тактовой частоты для микросхем, созданных на базе поколений технологии, представленных на рисунке 2 |

Срок, в течение которого сохранятся закономерности уменьшения транзисторов, зависит, в основном, от туннельного эффекта и от способности справляться с эффектом «короткого канала». Когда размеры транзистора уменьшаются без соответствующего понижения температуры, необходимого для уменьшения тока выключения, напряжение питания, пороговое напряжение и профиль распределения легирующей примеси необходимо подбирать так, чтобы сохранять приемлемое отношение тока включения к току выключения. На каком-то этапе туннельный и иные эффекты ограничивают длину канала настолько, что дальнейшее повышение производительности становится невозможным.

Таким образом, туннельный эффект является основным фактором, ограничивающим уменьшение транзистора. Предел находится примерно на уровне 1-1,5 нм; современные же транзисторы имеют топологические размеры в 3,5 мм. Подзатворный оксид в таком транзисторе будет иметь толщину всего в пять-шесть слоев атомов. Результаты недавних исследований [8] показывают, что туннелирующие токи могут вызвать повреждения, способные привести к возникновению непредвиденных ранее проблем с надежностью слишком тонкого подзатворного диэлектрика. Из этих соображений толщину подзатворного оксида приходится ограничивать 1,5-2 нм. Для повышения производительности без дальнейшего утончения подзатворного оксида придется разрабатывать новые структуры транзисторов или новые подзатворные оксиды с более высокой диэлектрической проницаемостью. Теория миниатюризации, к сожалению, не дает советов, которыми можно было бы при этом руководствоваться. Так что в этом отношении пределы уменьшения КМОП-элементов будут достигнуты очень скоро.

Фундаментальные ограничения, такие как тепловое движение носителей тока в твердом теле или принцип неопределенности, как показал Мейндл [9], практической роли не играют. Больший практический интерес представляют ограничения, связанные с созданием новых типов транзисторов. Независимо от конкретной структуры предельное минимальное расстояние между стоком и истоком с отношением тока включения к току выключения, равным 1000, за счет одного только туннельного перехода оказывается равным около 5 нм.

С учетом флуктуаций концентрации примесей и эффекта экранирования, этот предел достигает 10 нм. Выводы Мейндла еще менее оптимистичны: по его мнению, предел составляет порядка 25 нм. Так или иначе до того, как будут достигнуты пределы, в лучшем случае можно рассчитывать еще на 10-кратное уменьшение топологических размеров, которое при нынешних темпах займет около 15 лет. Технические проблемы уменьшения топологических размеров КМОП после уровня в 0,1 нм подробно освещены в других статьях журнала IBM Journal Research and Development [10].

Без изменений в структуре транзисторов их уменьшение при сохранении рабочей температуры на уровне комнатной приведет к замедлению темпов роста производительности уже через несколько лет. Но сложность изменения структуры чрезвычайно высока. Исторически такие перемены, как переход от металлических затворов к поликремниевым, переход от диффузии к внедрению ионов, всегда сопровождались огромными трудностями, хотя сама по себе структура транзисторов изменилась не сильно. Перейти на принципиально новую структуру будет еще сложнее.

Необходимо рассмотреть два типа изменений в структуре и материалах. Первое: существуют структуры, допускающие изготовление транзисторов с меньшей длиной канала. Второе: существуют материалы, обеспечивающие более высокую производительность при фиксированной длине канала.

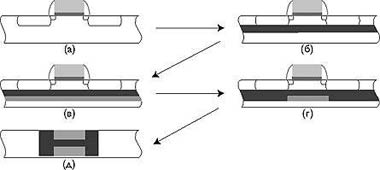

|

| Рис. 4. Прогнозируемое развитие транзисторных

структур приведет к появлению более симметричной структуры, которая

позволит улучшить управление полями в области затвора, регулирующими

условия работы транзистора На рисунке изображены следующие экспериментальные структуры: (а) монолитная кремниевая, (б) "кремний на изоляторе" (SOI), (в) земляной слой, счетчик-электрод, (г) вертикальный двойной затвор, (д) полностью симметричный двойной затвор. |

На рис. 4 показан ряд экспериментальных структур, обеспечивающих возможность перехода к меньшей длине канала. Первая – устройство типа «кремний на изоляторе», в отличие от стандартного транзистора на монолитной подложке. Подобная структура была разработана десятки лет назад, но лишь недавно концентрация дефектов, возникающих в связи с повреждениями при внедрении изолятора или каких-то иных методах его формирования, снизилась настолько, чтобы эту структуру стало можно применять. IBM обладает значительным опытом создания подобных транзисторов, из которого следует, что достижимый прирост производительности составляет 20-30%. Транзисторы можно уменьшить за счет применения технологии «кремний на изоляторе», но, по-видимому, лишь ненамного по сравнению с традиционными.

Две следующих структуры используют земляной слой – размещаемый под каналом транзистора проводящий слой какого-либо типа, действующий в качестве электростатического «зеркала», повышающего пропускную способность канала. Обе они представляют собой промежуточный этап на пути к двухзатворному транзистору, изображенному в низу рис. 1. Эта структура, по сути, имеет два канала (по одному на каждый интерфейс затвор – кремний), что обеспечивает удвоение мощности по сравнению с обычным транзистором и симметричность конструкции, которая позволяет свести к минимуму эффекты короткого канала. К сожалению, пока еще нельзя с уверенностью сказать, можно ли изготовить такие устройства на практике. Измерения, проведенные в ходе имитации работы такого транзистора, показали, что если его можно будет создать в ближайшие 15 лет, рост производительности транзисторов с большой вероятностью сохранит темпы 90-х годов (рис. 5).

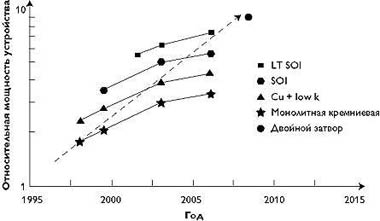

|

| Рис. 5. Использование новых структур и материалов

согласуется с тенденцией (пунктирная линия) экспоненциального роста

производительности транзисторов На рисунке изображены такие транзисторные структуры, как монолитная кремниевая и с двойным затвором. Графики, помеченные как SOI и LT SOIЮ, показывают использование структур "кремний на изоляторе" при комнатной и пониженной температурах соответственно, а Cu + low k показывает использование медных металлических межсоединений и изоляторов с малой диэлектрической проницаемостью. |

Еще один класс устройств базируется на применении новых материалов, повышающих подвижность носителей тока и, соответственно, производительность при фиксированной длине канала. К примеру, можно было бы формировать специальным образом искривленные кремниевые или кремниево-германиевые слои для повышения подвижности либо электронов, либо дырок. Одновременное улучшение подвижности электронов и дырок потребует довольно сложной структуры слоев. Повышение производительности может находиться в пределах от 30 до 60%. Пока не ясно, можно ли эти материалы применять с структурами с коротким каналом, описанными выше.

В принципе невозможность снизить рабочую температуру соразмерно с другими параметрами ограничивает степень уменьшения транзисторов. Следовательно, за счет снижения рабочей температуры можно было бы повысить производительность. Эффект был тщательно изучен рядом компаний во главе с IBM. Очевидно, что повышение производительности до двукратного может быть достигнуто при понижении рабочей температуры до уровня температуры жидкого азота (-195 С). Однако коммерческую реализацию идеи затрудняют проблемы, связанные со стоимостью и надежностью холодильников, а также потребностью в перепроектировании систем для оптимальной работы в низкотемпературном режиме.

Исторически всегда выгоднее было применять более традиционные способы повышения производительности, сохраняя рабочую температуру на уровне комнатной. Сейчас, учитывая возросшую трудность уменьшения размеров транзисторов, а также совершенствование методов охлаждения и кремниевой технологии как таковой, применение низкотемпературного режима может иметь смысл с коммерческой точки зрения, по крайней мере, для серверов старшего класса. Экономическая эффективность может быть достигнута при температуре -50° С, – при ней системы охлаждения смогут работать достаточно надежно, а большие изменения в кремниевой технологии не потребуются. Согласно оценкам, при такой температуре прибавка в производительности составит примерно 50%. В более отдаленном будущем для повышения производительности вдвое можно было бы опустить рабочую температуру до уровня жидкого азота, но для этого придется разработать КМОП с низким пороговым напряжением, а также специальные корпуса и криогенные охладители.

Лучшими кандидатами на работу при низких температурах считаются серверы старшего класса, но при своей высокой потребляемой мощности они требуют и довольно мощных систем охлаждения. Микросхемы можно охлаждать термоэлектрическими материалами, но их допустимо использовать лишь для обеспечения разницы температур в несколько десятков градусов и при уровнях потребляемой мощности в десятки ватт максимум. Тем не менее, даже за счет этого метода возможно достичь некоторого повышения производительности. Повысить производительность можно также путем обеспечения дополнительного охлаждения при установке портативных систем в док-станции. Все это дает почву для дальнейших исследований.

Все виды транзисторов, перечисленные выше, обеспечивают большую производительность при низкой температуре, хотя эффект, возможно, будет изменяться в зависимости от конкретного решения. Повысить производительность можно также за счет значительного снижения сопротивления и электрической емкости межэлементных соединений. Теоретический рост производительности со временем за счет работы в низкотемпературном режиме показан на рис. 5.

Проводники, соединяющие транзисторы, должны уменьшаться в размерах такими же темпами, что и сами транзисторы. В настоящее время индустрия переходит с аллюминиевой на медную разводку, отличающуюся одновременно более низкими сопротивлением и электрической емкостью. Идет изучение возможности замены материала междуслойных изоляторов, в качестве которого применяется диоксид кремния, на различные вещества с малой диэлектрической проницаемостью, далее снижающие емкость разводки. Несмотря на эти серьезные изменения, по-прежнему существует опасность, что высокие сопротивление и емкость крайне маленьких проводников сведут на нет прибавку в производительности, достигнутую за счет транзисторов. В качестве решения можно применять иерархическую структуру, когда первые несколько слоев содержат разводку высокой плотности, а далее идут слои с более крупной разводкой, отличающейся более низким сопротивлением и электрической емкостью. Такая иерархия одновременно отвечает потребностям в плотности и производительности. При таком подходе возможно создание интегральных схем с любой плотностью разводки, допускаемой литографией и конструкциями транзисторов, обсуждавшимися выше. Подробное обсуждение развития межэлементных соединений можно найти в другой статье данного выпуска журнала [11].

Развитие технологии КМОП – классический случай повышения степени интеграции за счет роста плотности. До сих пор мы обсуждали роль литографии, конструкции транзисторов и структуры межэлементных соединений, как средств повышения числа элементов на кристалл с целью достижения экономического эффекта снижения стоимости на функцию. Однако ключевую роль в превращении КМОП в доминирующую технологию сыграл фактор рассеиваемой мощности.

Современным полевым КМОП-транзисторам предшествовали метал-оксидные полупроводниковые (МОП) транзисторы n-типа, применявшиеся в 70-х, и МОП-транзисторы p-типа, которые появились в 60-х годах. Полевые транзисторы p-типа поначалу широко использовались ввиду их низкой чувствительности к подвижным ионам загрязняющих примесей наподобие натрия. Однако полевые транзисторы n-типа работают значительно быстрее, поскольку подвижность электронов гораздо выше, чем подвижность дырок. Индустрия быстро научилась разрабатывать эффективные чистые помещения и системы контроля загрязнения, чем обеспечила возможность перехода на транзисторы n-типа. Для повышения эффективности схем применялись обедненные и обогащенные полевые транзисторы. В современных КМОП-схемах транзисторы n-типа и p-типа применяются в сочетаниях, в значительной степени позволяющих снизить потребляемую мощность. Основные недостатки КМОП заключались в усложненности производственного процесса, несколько меньшей, по сравнению со схемами на биполярных транзисторах, производительностью и тенденции к запиранию. Запирание (latch-up), или блокирование схемы в сильноточном режиме, происходило из-за паразитного влияния транзисторов. Преимуществами КМОП были возможность интеграции большего числа функций и меньшая рассеиваемая мощность. В конце концов благодаря последнему фактору стала возможной большая, чем обеспечивалась транзисторами n-типа, плотность упаковки элементов интегральных схем. Были разрешены проблемы обработки, за счет современных схемотехнических решений была обойдена проблема запирания. Произошла решительная победа плотности над производительностью – плотность более медленного семейства схем повышалась достаточно быстро, чтобы компенсировать его недостатки.

В то время как полевые транзисторы использовались там, где требовалась ценовая эффективность, на рынке высокопроизводительных полупроводниковых систем доминировали схемы на биполярных транзисторах. Поскольку биполярные транзисторы в отличие от полевых размещались вертикально, а не горизонтально, они занимали гораздо меньше места. Более того, поскольку в отличие от полевых они работали в токовом режиме, общая производительность биполярных транзисторов была значительно выше. Они могли переключать ток гораздо быстрее, и, когда речь шла о схемах высокой производительности, выбор между КМОП и биполярными транзисторами однозначно делался в пользу последних. Однако к началу 90-х годов стало понятно, что рост числа элементов на кристалле может привести и к повышению производительности системы, и к снижению стоимости на элемент. При высокой степени интеграции функции, обычно требовавшие нескольких микросхем и сложных системных соединений, можно было реализовать на одном КМОП-кристалле. Результирующим эффектом стало повышение производительности микросхем и значительное снижение стоимости. Несмотря на преимущество в производительности биполярные схемы характеризуются по сравнению с КМОП гораздо большей рассеиваемой мощностью, а значит, и меньшей плотностью упаковки. Со временем, благодаря высокому уровню интеграции, технология КМОП достигла большей общей производительности несмотря на использование более медленных транзисторов.

Переход хорошо иллюстрирован рисунком 6 и таблицей 1 на примере систем IBM S/390. Системы G6, поставки которых начались в 1999 году, имеют вдвое с лишним большую производительность по сравнению с самой быстрой из существующих биполярных, но содержат гораздо меньше компонентов, занимают гораздо меньше места и расходуют меньше электроэнергии.

Что произойдет с КМОП-схемами в будущем? Будут ли они когда-то вытеснены другим семейством схем, благодаря чему произойдет новый качественный скачок в развитии интегральных схем? На данный момент, похоже, жизнеспособной альтернативы КМОП не существует. Полевые транзисторы несколько десятилетий применялись в недорогих несложных устройствах, прежде чем достигли той степени развития, когда ими стало можно заменить биполярные транзисторы в системах высокой производительности. Однако технологии, которая бы в настоящее время развивалась в секторе экономически эффективных устройств, и могла бы вытеснить со временем КМОП, нет. Кроме того, учитывая непрерывную эволюцию КМОП-технологии, альтернативная технология, способная ее заменить, должна была бы развиваться еще быстрее. Возможно, появятся какие-то новые разновидности КМОП-схем, но радикальной смены типа схем пока не предвидится.

Альтернативы КМОП-технологии предлагаются и исследуются. Во многих из них также взят за основу кремний. Большинство таких альтернатив предназначены для выполнения иных, по сравнению с КМОП, функций, и поэтому с большей вероятностью они добьются успеха лишь в узких нишах. Так что в области вычислительных систем общего назначения и обработки данных в обозримом будущем КМОП, по-видимому, сохранит доминирующее положение.

Память – важнейшая часть системы на КМОП-схемах; ее объем и производительность должны расти параллельно мощности процессора. Микросхема DRAM состоит из КМОП-логики и ячеек, каждая из которых представляет собой сочетание из транзистора и конденсатора. В экономическом отношении индустрия DRAM следовала закону Мура точнее, чем любая другая индустрия. В течение 20 лет непрерывно появлялись новые поколения модулей DRAM, и сейчас число бит на кристалл увеличивается в четыре раза каждые 3 года. Как и предсказывал Мур, наполовину развитие происходило за счет разрешающей способности литографии, на четверть – за счет увеличения размера кристалла, и на остающуюся четверть – за счет инноваций. Литографию мы обсудили выше, о размерах кристаллов кратко говорится в разделе о стоимости. Инновации в области ячеек памяти заслуживают более пристального рассмотрения.

До «мегабитного» поколения включительно в микросхемах динамической памяти использовались однотранзисторные планарные ячейки. Транзистор и конденсатор, формирующие ячейку, располагались обычным образом, бок о бок. Уменьшить размер ячейки независимо от литографического процесса позволили новые конструктивные решения, такие как самосовмещение и нестандартная топология. В поколении микросхем памяти на 4 Мбит IBM использует изобретенные ею особые ячейки, в которых конденсатор формируется в подложке вертикально, а не горизонтально. Некоторые производители применяют многоуровневое размещение конденсаторов, при котором конденсаторы также формируются вертикально, но размещаются поверх кремниевой пластины. Оба подхода преобладают по сей день. В части инноваций закон Мура реализуется за счет уменьшения зазора между конденсатором и транзистором, располагаемыми один поверх другого.

Традиционные конструктивные решения ограничивают площадь ячейки квадратом толщины литографической линии, помноженным на восемь. Этот предел будет достигнут с появлением микросхем DRAM емкостью 1 Гбайт. Благодаря новым архитектурным подходам коэффициент может понизиться до шести или даже до четырех. Однако квадрат минимального топологического размера, помноженный на четыре – это физический предел. Т. е., если расположение ячейки определяется пересечением двух перпендикулярных линий минимального размера, и если ячейка отстоит от соседней на минимальный размер, то минимальная площадь ячейки будет в четыре раза больше квадрата минимального размера. На такой площади поистине очень сложно уместить сток, исток, затвор транзистора и конденсатор. Для преодоления барьера потребуются схемы, хранящие более одного бита в ячейке, а они вряд ли появятся, поскольку обеспечиваемое ими преимущество в площади, скорее всего, будет сведено на нет понижением отношения сигнал-шум.

Следовательно, ячейки памяти можно уменьшать в соответствии с законом Мура только до тех пор, пока растет разрешающая способность литографии, и пока их площадь будет меньше четырех литографических квадратов. После этого (или даже раньше, если за счет инноваций не будет преодолен барьер в шесть квадратов), уменьшение размера ячейки будет происходить исключительно за счет совершенствования процесса литографии. Если оно тоже замедлится, прогресс в технологиях памяти может остановиться.

Экономика DRAM может продиктовать и иной сценарий. Закон Мура, по сути, утверждает, что для его сохранения стоимость на бит должна падать. Если издержки на литографию или процесс изготовления перестанут оправдывать результирующее повышение плотности бит, дальнейший рост емкости DRAM может оказаться экономически не эффективным. Или, если с появлением какого-то из поколений DRAM исчезнет массовый спрос на память, есть вероятность, что стоимость ее разработки и производства не удастся амортизировать за счет достаточного объема выпуска. Подобные экономические ножницы прогнозировались для многих поколений DRAM, но пока еще ни разу не возникли. Поскольку приложения непрерывно развиваются, и потребности компьютеров массового производства в памяти уже измеряются гигабайтами, такого, быть может, не произойдет никогда.

Основное внимание закон Мура уделяет числу элементов на кристалле. В своей первой публикации Мур не предвидел, что когда-то появятся микросхемы с миллиардом транзисторов, продаваемые менее чем за 100 долл. Сейчас до их появления осталось, быть может, не более двух лет. Однако функции, выполняемые этими транзисторами, зависят от структуры микросхемы, т. е. от логики соединений транзисторов. При столь огромном количестве элементов число возможных вариантов структуры может быть практически бесконечным. Все транзисторы могут иметь разные длину и ширину канала, разное пороговое напряжение. Каждый можно соединить чуть ли не с любым другим на интегральной схеме. Число комбинаций просто непостижимо. Искусство схемотехники состоит в выборе той из комбинаций, которая выполняет определенную функцию. Эти функции благодаря развитию технологий могут быть настолько сложными, что автоматизация проектирования и верификация структуры интегральных схем становятся для эволюции КМОП-технологии факторами не менее важными, чем процесс изготовления.

Если в законе Мура главным было число транзисторов на кристалле, то сейчас более уместно говорить о функциях, выполняемых этими транзисторами. Современные методики проектирования позволяют без дальнейшего увеличения числа транзисторов повысить количество функций на кристалл. Следовательно, закон Мура необходимо переформулировать так, чтобы он говорил о росте функциональности, а не количества транзисторов. Как было замечено выше, чтобы темпы роста функциональности оставались на прежнем уровне, число транзисторов не обязательно должно расти столь же быстро, как и раньше. Темпы роста в законе Мура уже менялись ранее, и, скорее всего, изменятся еще раз, но на рост функциональности это существенно не повлияет. Замедление темпов роста числа транзисторов, по всей видимости, мало отразится на тенденциях развития индустрии ввиду наличия огромного потенциала в области схемотехнических решений и увеличения количества функций на фиксированное число транзисторов.

В одном – развитие конструкции микросхем, похоже, противоречит Закону Мура. Современные микропроцессоры не только умещаются на одном кристалле, но, по сути, занимают лишь небольшой его участок. Остающаяся его часть обычно используется под кэш-память, которая увеличивает стоимость процессора, но с другой стороны обеспечивает существенную прибавку в производительности. Размеры процессора приходится уменьшать из-за увеличения числа транзисторов на единицу площади, а не общего числа транзисторов, требуемых для процессора. С ростом тактовой частоты допустимые габариты процессора уменьшаются быстрее, чем реальные размеры. Их тактовая частота скоро будет исчисляться гигагерцами. Для 10-гигагерцевого процессора, который, возможно, появится к 2010 году, время такта составит 100 пс. Поскольку скорость света в вакууме составляет 0,3 мм/пс, то за 1 такт свет может пройти 30 мм. В среде же, состоящей из типичного диэлектрика, свет пройдет порядка 15-20 мм, что примерно соответствует размеру современного кристалла. Согласно фундаментальным законам физики, за определенное время информацию нельзя передать на расстояние большее, чем за то же время может пройти свет. Из-за практических ограничений в реальности предел расстояния передачи еще меньше. К счастью, метод иерархической разводки позволяет разместить все высокочастотные части схемы на небольшой площади, и выполнять передачу информации на большие расстояния за более длинные такты. Тем не менее ограничение по размеру – серьезное препятствие на пути дальнейшего выполнения закона Мура в части роста размера кристалла.

Уменьшение стоимости – один из основных аспектов закона Мура. Основная движущая сила снижения стоимости на схему или бит памяти – повышение плотности, или числа схем на квадратный миллиметр. Чтобы расходы уменьшались, стоимость обработки кремниевой подложки должна повышаться гораздо медленнее, чем плотность. Происходившее в 80-е годы быстрое (на 25% ежегодно) увеличение капитальных расходов на производственные линии привело к появлению опасности прекращения ответного падения стоимости на схему. Однако, начиная с 1990 года, темпы повышения расходов замедлились — менее чем до 15% в год. В основном это произошло благодаря стабилизации требований к чистым производственным помещениям, повышению продуктивности оборудования и уровня утилизации отходов, а также замедлению темпов усложнения обработки. Основную долю издержек при выпуске интегральных схем составляют капитальные расходы на создание оборудования и чистых производственных помещений. Темпы повышения этих расходов должны перекрываться темпами увеличения числа элементов на кристалл. Пока рост числа элементов на кристалл используется эффективными схемотехническими решениями для расширения функциональности, компьютерная индустрия продолжит процветать.

Главный вывод данной статьи состоит в том, что технология КМОП, по всей видимости, продолжит свое развитие и будет доминировать еще в течение ближайших 10-15 лет. Однако на пути развития каждой из составляющих технологии стоят серьезные препятствия. Потребуется радикальное расширение возможностей оптической литографии и, вероятно, переход на неоптические методы. Необходимы также принципиально новые конструкции транзисторов и материалы, используемые для их формирования. Чтобы добиться экономически эффективного увеличения степени интеграции микросхем памяти, придется разработать принципиально новые структуры и для ячеек DRAM. Проводники должны достигнуть размеров в десятые доли микрона, и формировать их придется в тщательным образом спроектированных иерархических структурах на основе материалов с низкой диэлектрической проницаемостью. Динамические схемы и ячейки статической оперативной памяти необходимо проектировать так, чтобы их функциональность при фиксированном числе транзисторов возрастала. Снижение расходов по-прежнему будет зависеть от способности интегрировать больше функций на кристалл. Это потребует серьезных скачков в развитии средств автоматизации проектирования и разработки технологии, оптимальной для интеграции систем.

Все указанные области характеризуются огромным потенциалом. Наиболее перспективным направлением дальнейшего развития мне видится способность к интеграции систем. Основным компонентом вычислительных систем будущего станет не микропроцессор, а однокристалльная микросистема, реализующая большее число функций. Высокоскоростные процессоры необходимо проектировать в контексте остальной частью системы и сообразно ее особенностям. При условии существенных подвижек в перечисленных областях индустрия сумеет сохранить действие закона Мура если не в плане конкретных цифр, то по крайней мере в плане его сути.

Я хотел бы поблагодарить своих коллег за идеи и мнения, изложенные в данной статье. Отдельное спасибо сотрудникам IBM Тэку Нингу, Рассу Лангу, Биджану Давари и Бобу Деннарду за их деятельное участие и конструктивные советы. Я также хочу поблагодарить Майка Полкари, Джона Уорлормонта, Юана Таура, Тома Тейса и Джорджа Гомба за полезные консультации.

IBM Technical Journals Journal of Research and Development, Vol. 44, No. 3, Special Issue — Directions in information technology. R.D. Isaac, The future of CMOS technology.

Copyright IBM, 2000. Перевод публикуется с разрешения корпорации IBM. Все права сохранены.

| Технология | ES/9000 9X2 Биполярная | S/390 G6 КМОП |

| Общее число микросхем | 5000 | 31 |

| Общее число компонентов | 6659 | 92 |

| Вес, кг | 14109 | 932 |

| Потребляемая мощность, кВА | 153 | 5,5 |

| Кристаллов на процессор | 390 | 1 |

| Максимальная емкость памяти, Гбайт | 10 | 32 |

| Занимаемая площадь, м2 | 62,3 | 4,8 |